उत्पाद श्रेणी

- एफएम ट्रांसमीटर

- 0-50w 50w-1000w 2kw-10kw 10kw +

- टीवी ट्रांसमीटर

- 0-50w 50-1kw 2kw-10kw

- एफएम एंटीना

- टीवी एंटीना

- एंटीना गौण

- केबल योजक पावर अलगानेवाला डमी भार

- आरएफ ट्रांजिस्टर

- बिजली की आपूर्ति

- ऑडियो उपकरण

- DTV फ्रंट एंड उपकरण

- लिंक सिस्टम

- एसटीएल प्रणाली माइक्रोवेव लिंक प्रणाली

- एफएम रेडियो

- बिजली मीटर

- अन्य उत्पाद

- कोरोनावायरस के लिए विशेष

उत्पाद टैग

Fmuser साइटें

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net -> अफ्रीकी

- sq.fmuser.net -> अल्बानियाई

- ar.fmuser.net -> अरबी

- hy.fmuser.net -> अर्मेनियाई

- az.fmuser.net -> अजरबैजानी

- eu.fmuser.net -> बास्क

- be.fmuser.net -> बेलारूसी

- bg.fmuser.net -> बल्गेरियाई

- ca.fmuser.net -> कातालान

- zh-CN.fmuser.net -> चीनी (सरलीकृत)

- zh-TW.fmuser.net -> चीनी (पारंपरिक)

- hr.fmuser.net -> क्रोएशियाई

- cs.fmuser.net -> चेक

- da.fmuser.net -> डेनिश

- nl.fmuser.net -> डच

- et.fmuser.net -> एस्टोनियाई

- tl.fmuser.net -> फिलिपिनो

- fi.fmuser.net -> फिनिश

- fr.fmuser.net -> फ्रेंच

- gl.fmuser.net -> गैलिशियन्

- ka.fmuser.net -> जॉर्जियाई

- de.fmuser.net -> जर्मन

- el.fmuser.net -> यूनानी

- ht.fmuser.net -> हाईटियन क्रियोल

- iw.fmuser.net -> हिब्रू

- hi.fmuser.net -> हिन्दी

- hu.fmuser.net -> हंगेरी

- is.fmuser.net -> आइसलैंड का

- id.fmuser.net -> इन्डोनेशियाई

- ga.fmuser.net -> आयरिश

- it.fmuser.net -> इतालवी

- ja.fmuser.net -> जापानी

- ko.fmuser.net -> कोरियाई

- lv.fmuser.net -> लातवियाई

- lt.fmuser.net -> लिथुआनियाई

- mk.fmuser.net -> मकदूनियाई

- ms.fmuser.net -> मलय

- mt.fmuser.net -> माल्टीज

- no.fmuser.net -> नार्वेजियन

- fa.fmuser.net -> फारसी

- pl.fmuser.net -> पॉलिश

- pt.fmuser.net -> पुर्तगाली

- ro.fmuser.net -> रोमानियाई

- ru.fmuser.net -> रूसी

- sr.fmuser.net -> सर्बियाई

- sk.fmuser.net -> स्लोवाक

- sl.fmuser.net -> स्लोवेनियाई

- es.fmuser.net -> स्पेनिश

- sw.fmuser.net -> स्वाहिली

- sv.fmuser.net -> स्वीडिश

- th.fmuser.net -> थाई

- tr.fmuser.net -> तुर्की

- uk.fmuser.net -> यूक्रेनी

- ur.fmuser.net -> उर्दू

- vi.fmuser.net -> वियतनामी

- cy.fmuser.net -> वेल्श

- yi.fmuser.net -> येहुदी

हाफ एडर क्या है: सर्किट आरेख और उसके अनुप्रयोग

Date:2021/10/18 21:55:58 Hits:

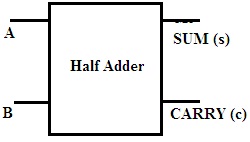

हाफ एडर एक तरह का बेसिक डिजिटल सर्किट है। इससे पहले एनालॉग सर्किट में विभिन्न ऑपरेशन किए जाते हैं। डिजिटल इलेक्ट्रॉनिक्स की खोज के बाद इसमें इसी तरह के ऑपरेशन किए जाते हैं। डिजिटल सिस्टम को प्रभावी और विश्वसनीय माना जाता है। विभिन्न संक्रियाओं में सबसे प्रमुख संक्रियाओं में से एक अंकगणित है। इसमें जोड़, घटाव, गुणा और भाग शामिल हैं। हालाँकि, यह पहले से ही ज्ञात है कि यह एक कंप्यूटर हो सकता है, कैलकुलेटर जैसा कोई भी इलेक्ट्रॉनिक गैजेट गणितीय संचालन कर सकता है। ये ऑपरेशन किए जाते हैं जिनमें बाइनरी मान होते हैं। इसमें कुछ सर्किट की उपस्थिति से यह संभव है। इन सर्किटों को बाइनरी एडर्स और सबट्रैक्टर्स के रूप में जाना जाता है। इस प्रकार के सर्किट बाइनरी कोड, अतिरिक्त -3 कोड और अन्य कोड के लिए भी डिज़ाइन किए गए हैं। इसके अलावा बाइनरी एडर्स को दो प्रकारों में वर्गीकृत किया गया है। वे हैं: आधा योजक और पूर्ण योजक एक आधा योजक क्या है? एक डिजिटल इलेक्ट्रॉनिक सर्किट जो बाइनरी नंबरों पर जोड़ करने के लिए कार्य करता है उसे आधा योजक के रूप में परिभाषित किया जाता है। जोड़ की प्रक्रिया इनकार है एकमात्र अंतर चुनी गई संख्या प्रणाली है। बाइनरी नंबरिंग सिस्टम में केवल 0 और 1 होता है। संख्या का भार पूरी तरह से द्विआधारी अंकों की स्थिति पर आधारित होता है। उन 1 और 0 में, 1 को सबसे बड़ा अंक माना जाता है और 0 को छोटा माना जाता है। इस योजक का ब्लॉक आरेख है आधा योजकआधा योजक सर्किट आरेखएक आधा योजक में दो इनपुट होते हैं और दो आउटपुट उत्पन्न करते हैं। इसे सबसे सरल डिजिटल सर्किट माना जाता है। इस सर्किट के इनपुट वे बिट्स हैं जिन पर जोड़ किया जाना है। प्राप्त आउटपुट योग और कैरी हैं।

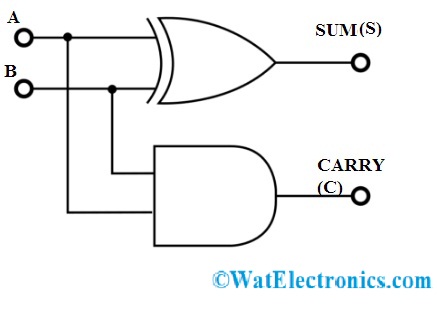

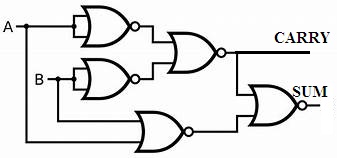

आधा योजकआधा योजक सर्किट आरेखएक आधा योजक में दो इनपुट होते हैं और दो आउटपुट उत्पन्न करते हैं। इसे सबसे सरल डिजिटल सर्किट माना जाता है। इस सर्किट के इनपुट वे बिट्स हैं जिन पर जोड़ किया जाना है। प्राप्त आउटपुट योग और कैरी हैं।  आधा योजकइस योजक के सर्किट में दो द्वार होते हैं। वे AND और XOR गेट हैं। सर्किट में मौजूद दोनों गेटों के लिए लागू इनपुट समान हैं। लेकिन आउटपुट हर गेट से लिया जाता है। XOR गेट के आउटपुट को SUM के रूप में संदर्भित किया जाता है और AND के आउटपुट को CARRY कहा जाता है। हाफ एडर ट्रुथ टेबल लागू इनपुट से प्राप्त आउटपुट के संबंध को प्राप्त करने के लिए ट्रुथ टेबल के रूप में जानी जाने वाली तालिका का उपयोग करके विश्लेषण किया जा सकता है।

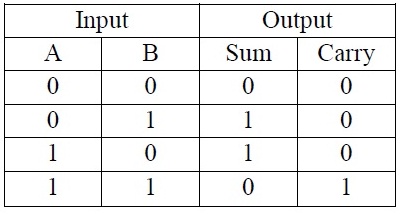

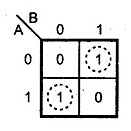

आधा योजकइस योजक के सर्किट में दो द्वार होते हैं। वे AND और XOR गेट हैं। सर्किट में मौजूद दोनों गेटों के लिए लागू इनपुट समान हैं। लेकिन आउटपुट हर गेट से लिया जाता है। XOR गेट के आउटपुट को SUM के रूप में संदर्भित किया जाता है और AND के आउटपुट को CARRY कहा जाता है। हाफ एडर ट्रुथ टेबल लागू इनपुट से प्राप्त आउटपुट के संबंध को प्राप्त करने के लिए ट्रुथ टेबल के रूप में जानी जाने वाली तालिका का उपयोग करके विश्लेषण किया जा सकता है। आधा योजक सत्य तालिका उपरोक्त सत्य तालिका से अंक निम्नानुसार स्पष्ट हैं: यदि ए = 0, बी = 0 जो कि दोनों इनपुट लागू होते हैं 0. फिर दोनों आउटपुट एसयूएम और कैरी 0 हैं। दो इनपुट में से कोई भी लागू होता है इनपुट 1 है तो SUM b e1 होगा लेकिन CARRY 0 है। यदि दोनों इनपुट 1 हैं तो SUM 0 के बराबर होगा और CARRY 1 के बराबर होगा। इनपुट के आधार पर ऑपरेशन के साथ आधा योजक आय लागू होती है जोड़ का। समीकरण इस प्रकार के सर्किट के लिए समीकरण उत्पादों के योग (एसओपी) और योग के उत्पाद (पीओएस) की अवधारणाओं से महसूस किया जा सकता है। इस प्रकार के सर्किट के लिए बूलियन समीकरण प्राप्त आउटपुट के लिए लागू इनपुट के बीच संबंध को निर्धारित करता है। समीकरण को निर्धारित करने के लिए सत्य तालिका मूल्यों के आधार पर k-मानचित्र तैयार किए जाते हैं। इसमें दो समीकरण होते हैं क्योंकि इसमें दो लॉजिक गेट्स का उपयोग किया जाता है। कैरी का k-मैप है

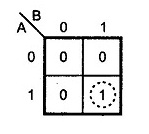

आधा योजक सत्य तालिका उपरोक्त सत्य तालिका से अंक निम्नानुसार स्पष्ट हैं: यदि ए = 0, बी = 0 जो कि दोनों इनपुट लागू होते हैं 0. फिर दोनों आउटपुट एसयूएम और कैरी 0 हैं। दो इनपुट में से कोई भी लागू होता है इनपुट 1 है तो SUM b e1 होगा लेकिन CARRY 0 है। यदि दोनों इनपुट 1 हैं तो SUM 0 के बराबर होगा और CARRY 1 के बराबर होगा। इनपुट के आधार पर ऑपरेशन के साथ आधा योजक आय लागू होती है जोड़ का। समीकरण इस प्रकार के सर्किट के लिए समीकरण उत्पादों के योग (एसओपी) और योग के उत्पाद (पीओएस) की अवधारणाओं से महसूस किया जा सकता है। इस प्रकार के सर्किट के लिए बूलियन समीकरण प्राप्त आउटपुट के लिए लागू इनपुट के बीच संबंध को निर्धारित करता है। समीकरण को निर्धारित करने के लिए सत्य तालिका मूल्यों के आधार पर k-मानचित्र तैयार किए जाते हैं। इसमें दो समीकरण होते हैं क्योंकि इसमें दो लॉजिक गेट्स का उपयोग किया जाता है। कैरी का k-मैप है  के-मैप और गेटकैरी का आउटपुट समीकरण और गेट से प्राप्त किया जाता है। सी = ए। एसयूएम के लिए बूलियन एक्सप्रेशन एसओपी फॉर्म द्वारा महसूस किया जाता है। इसलिए एसयूएम के लिए के-मानचित्र है

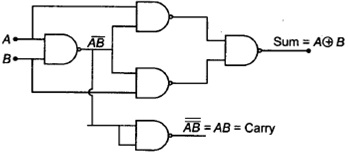

के-मैप और गेटकैरी का आउटपुट समीकरण और गेट से प्राप्त किया जाता है। सी = ए। एसयूएम के लिए बूलियन एक्सप्रेशन एसओपी फॉर्म द्वारा महसूस किया जाता है। इसलिए एसयूएम के लिए के-मानचित्र है योग के लिए K-मानचित्र (XOR) निर्धारित समीकरण हैS=A⊕ BAअनुप्रयोग इस मूल योजक के अनुप्रयोग इस प्रकार हैं बाइनरी बिट्स पर परिवर्धन करने के लिए कंप्यूटर में मौजूद अंकगणित और तर्क इकाई इस योजक सर्किट को पसंद करती है। आधे योजक सर्किट का संयोजन होता है पूर्ण योजक सर्किट के गठन के लिए। कैलकुलेटर के डिजाइन में इन तर्क सर्किटों को प्राथमिकता दी जाती है। पते और तालिकाओं की गणना करने के लिए इन सर्किटों को प्राथमिकता दी जाती है। केवल अतिरिक्त के बजाय, ये सर्किट डिजिटल सर्किट में विभिन्न अनुप्रयोगों को संभालने में सक्षम हैं। इसके अलावा, यह डिजिटल इलेक्ट्रॉनिक्स का दिल बन जाता है। वीएचडीएल कोड हाफ एडर सर्किटी के लिए वीएचडीएल कोड लाइब्रेरी है; ieee.std_logic_1164.all का उपयोग करें; इकाई आधा_एडर isport (ए, बी: बिट में; योग, कैरी: आउट बिट); अंत आधा_एडर हाफ_एडर का आर्किटेक्चर डेटा बेगिनसम है<= a xor b;कैरी <= a और b;एंड डेटा;अक्सर पूछे जाने वाले प्रश्न1। Adder से आपका क्या मतलब है? डिजिटल सर्किट जिसका एकमात्र उद्देश्य अतिरिक्त करना है, Adders के रूप में जाना जाता है। ये ALU के मुख्य घटक हैं। योजक संख्याओं के विभिन्न स्वरूपों के अतिरिक्त कार्य करते हैं। योजक के आउटपुट योग और कैरी हैं।२। हाफ एडर की सीमाएं क्या हैं? पिछले बिट से उत्पन्न कैरी बिट को जोड़ा नहीं जा सकता इस योजक की सीमा है। एकाधिक बिट्स के लिए अतिरिक्त प्रदर्शन करने के लिए इन सर्किटों को प्राथमिकता नहीं दी जा सकती है।2। NOR गेट का उपयोग करके हाफ एडर कैसे लागू करें? इस प्रकार के योजक का कार्यान्वयन NOR गेट का उपयोग करके भी किया जा सकता है। यह एक और यूनिवर्सल गेट है।

योग के लिए K-मानचित्र (XOR) निर्धारित समीकरण हैS=A⊕ BAअनुप्रयोग इस मूल योजक के अनुप्रयोग इस प्रकार हैं बाइनरी बिट्स पर परिवर्धन करने के लिए कंप्यूटर में मौजूद अंकगणित और तर्क इकाई इस योजक सर्किट को पसंद करती है। आधे योजक सर्किट का संयोजन होता है पूर्ण योजक सर्किट के गठन के लिए। कैलकुलेटर के डिजाइन में इन तर्क सर्किटों को प्राथमिकता दी जाती है। पते और तालिकाओं की गणना करने के लिए इन सर्किटों को प्राथमिकता दी जाती है। केवल अतिरिक्त के बजाय, ये सर्किट डिजिटल सर्किट में विभिन्न अनुप्रयोगों को संभालने में सक्षम हैं। इसके अलावा, यह डिजिटल इलेक्ट्रॉनिक्स का दिल बन जाता है। वीएचडीएल कोड हाफ एडर सर्किटी के लिए वीएचडीएल कोड लाइब्रेरी है; ieee.std_logic_1164.all का उपयोग करें; इकाई आधा_एडर isport (ए, बी: बिट में; योग, कैरी: आउट बिट); अंत आधा_एडर हाफ_एडर का आर्किटेक्चर डेटा बेगिनसम है<= a xor b;कैरी <= a और b;एंड डेटा;अक्सर पूछे जाने वाले प्रश्न1। Adder से आपका क्या मतलब है? डिजिटल सर्किट जिसका एकमात्र उद्देश्य अतिरिक्त करना है, Adders के रूप में जाना जाता है। ये ALU के मुख्य घटक हैं। योजक संख्याओं के विभिन्न स्वरूपों के अतिरिक्त कार्य करते हैं। योजक के आउटपुट योग और कैरी हैं।२। हाफ एडर की सीमाएं क्या हैं? पिछले बिट से उत्पन्न कैरी बिट को जोड़ा नहीं जा सकता इस योजक की सीमा है। एकाधिक बिट्स के लिए अतिरिक्त प्रदर्शन करने के लिए इन सर्किटों को प्राथमिकता नहीं दी जा सकती है।2। NOR गेट का उपयोग करके हाफ एडर कैसे लागू करें? इस प्रकार के योजक का कार्यान्वयन NOR गेट का उपयोग करके भी किया जा सकता है। यह एक और यूनिवर्सल गेट है। NOR Gates4 का उपयोग करते हुए आधा योजक। NAND गेट का उपयोग करके हाफ एडर को कैसे लागू करें? NAND गेट यूनिवर्सल गेट्स के प्रकारों में से एक है। यह इंगित करता है कि नंद द्वारों के उपयोग से किसी भी प्रकार की सर्किट डिजाइनिंग संभव है।

NOR Gates4 का उपयोग करते हुए आधा योजक। NAND गेट का उपयोग करके हाफ एडर को कैसे लागू करें? NAND गेट यूनिवर्सल गेट्स के प्रकारों में से एक है। यह इंगित करता है कि नंद द्वारों के उपयोग से किसी भी प्रकार की सर्किट डिजाइनिंग संभव है। आधा योजक उपरोक्त सर्किट से, एक NAND गेट के आउटपुट को अन्य NAND गेट के रूप में इनपुट पर लागू करके कैरी आउटपुट उत्पन्न किया जा सकता है। यह और कुछ नहीं बल्कि AND गेट से प्राप्त आउटपुट से परिचित है। SUM का आउटपुट समीकरण प्रारंभिक NAND गेट के आउटपुट को A और B के अलग-अलग इनपुट के साथ आगे NAND गेट्स पर लागू करके उत्पन्न किया जा सकता है। अंत में, उन नंद द्वारों द्वारा प्राप्त आउटपुट को फिर से गेट पर लागू किया जाता है। इसलिए एसयूएम के लिए आउटपुट उत्पन्न होता है। इसलिए डिजिटल सर्किट में मूल योजक को विभिन्न लॉजिक गेट्स का उपयोग करके डिज़ाइन किया जा सकता है। लेकिन कई बिट जोड़ जटिल हो जाते हैं और इसे आधे योजक की सीमा माना जाता है। क्या आप बता सकते हैं कि किसी भी व्यावहारिक काउंटर में वेतन वृद्धि संचालन के लिए किस आईसी का उपयोग किया जाता है?

आधा योजक उपरोक्त सर्किट से, एक NAND गेट के आउटपुट को अन्य NAND गेट के रूप में इनपुट पर लागू करके कैरी आउटपुट उत्पन्न किया जा सकता है। यह और कुछ नहीं बल्कि AND गेट से प्राप्त आउटपुट से परिचित है। SUM का आउटपुट समीकरण प्रारंभिक NAND गेट के आउटपुट को A और B के अलग-अलग इनपुट के साथ आगे NAND गेट्स पर लागू करके उत्पन्न किया जा सकता है। अंत में, उन नंद द्वारों द्वारा प्राप्त आउटपुट को फिर से गेट पर लागू किया जाता है। इसलिए एसयूएम के लिए आउटपुट उत्पन्न होता है। इसलिए डिजिटल सर्किट में मूल योजक को विभिन्न लॉजिक गेट्स का उपयोग करके डिज़ाइन किया जा सकता है। लेकिन कई बिट जोड़ जटिल हो जाते हैं और इसे आधे योजक की सीमा माना जाता है। क्या आप बता सकते हैं कि किसी भी व्यावहारिक काउंटर में वेतन वृद्धि संचालन के लिए किस आईसी का उपयोग किया जाता है?

एक संदेश छोड़ें

संदेश सूची

टिप्पणियां लोड हो रहा है ...